セルオートマトン型画像領域抽出回路

セルオートマトン方式の画素並列で動作する領域抽出アルゴリズムを考案し,

それをFPGAで実現しました。

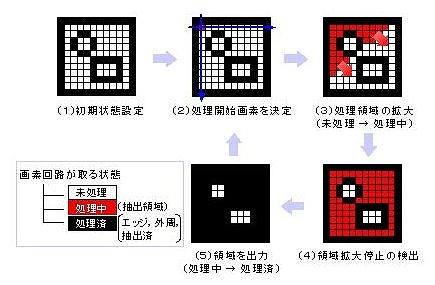

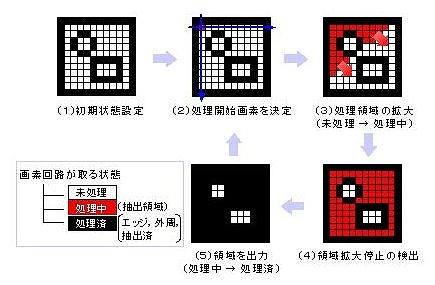

セルオートマトン型領域抽出アルゴリズム

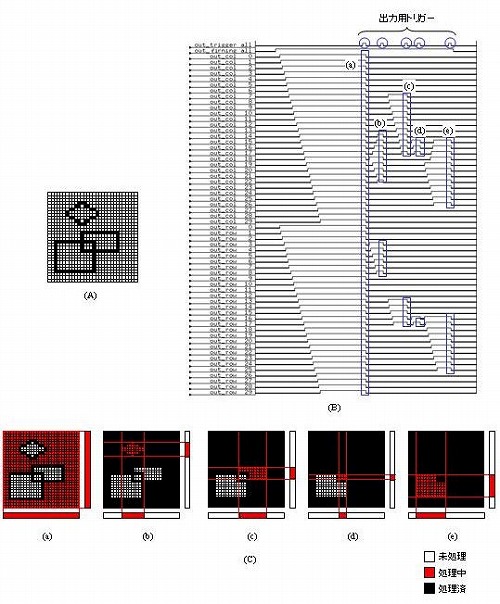

FPGA実装結果(測定結果)

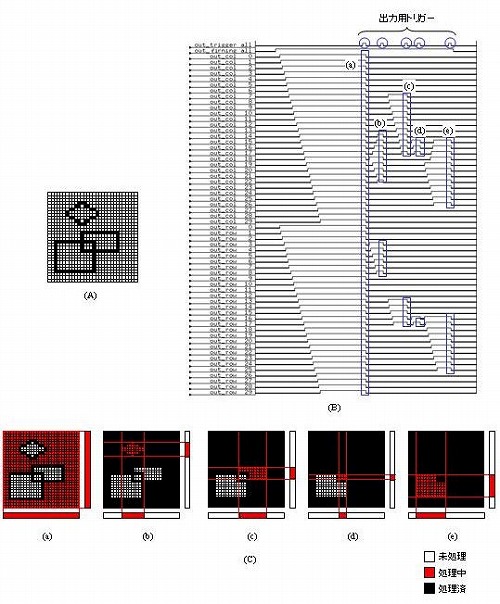

(A)入力パターン(抵抗ヒューズ処理により大局的領域分割を行った結果), (B)ロジックアナライザでの波形パターン,(C)抽出処理の様子

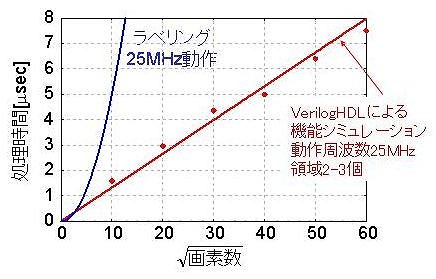

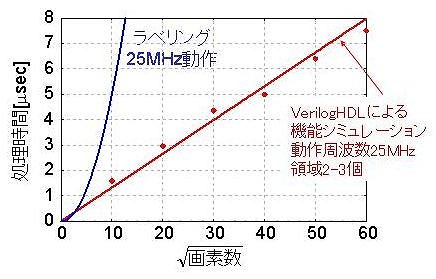

処理時間の見積(通常のラベリング処理との比較)

(最終更新日:2007/11/21)

セルオートマトン方式の画素並列で動作する領域抽出アルゴリズムを考案し,

それをFPGAで実現しました。

処理時間の見積(通常のラベリング処理との比較)

(最終更新日:2007/11/21)