Coarse region segmentation and resistive-fuse network circuits

Coarse region segmentation in human visual system

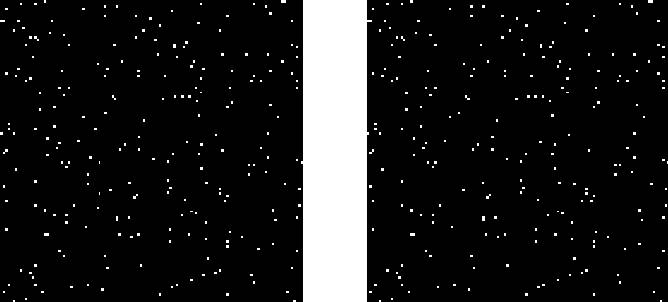

Sparse random dot stereogram (from Prof. Hanazawa)

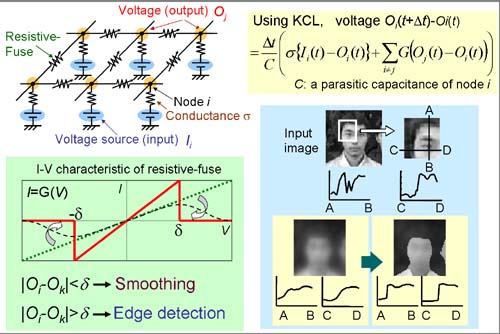

Resistive-fuse network circuits for coarse region segmentation

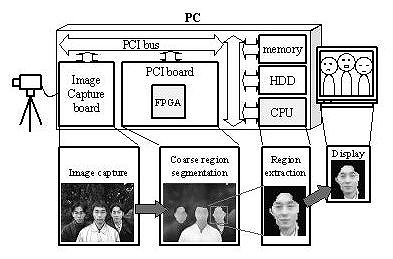

PC system using FPGA implementation of resistive-fuse networks

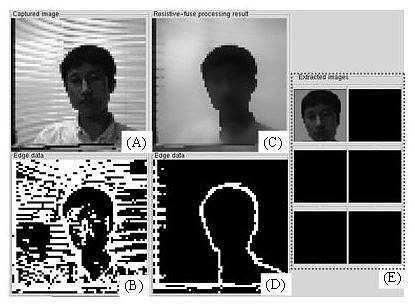

Coarse region segmentation demo (face)

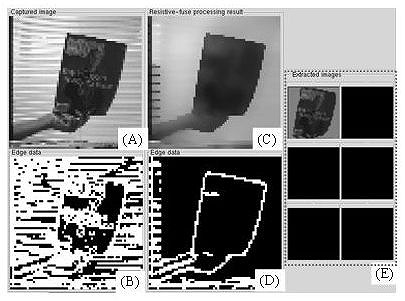

(A) input image (human standing in front of the window-shade),

(B) normal edge extraction result,

(C) resistive-fuse network processing result,

(D) edge extraction result of (C),

(E) region extraction results

Coarse region segmentation demo (book)

Pixel-parallel resistive-fuse network LSI using merged A/D architecture

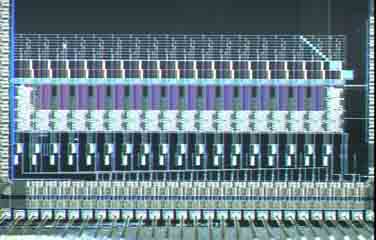

- 1D pixel-parallel resistive-fuse network LSI

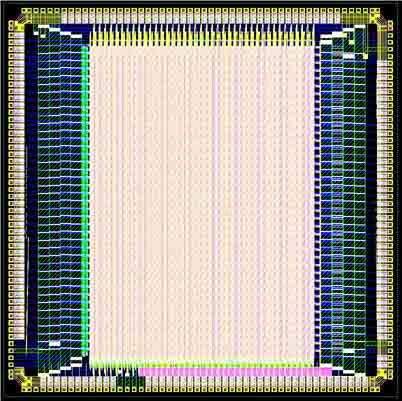

- 2D pixel-parallel resistive-fuse network LSI (chip size: 9 mm sq.)

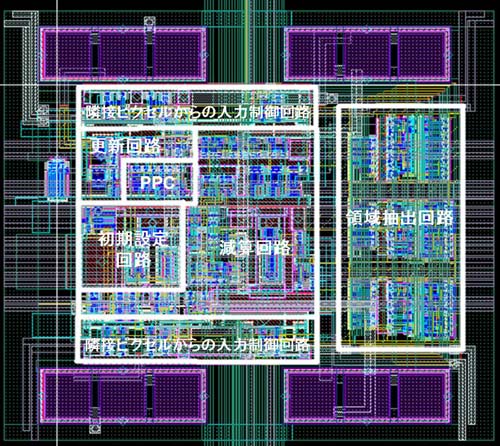

- Pixel circuit layout result for 2D pixel-parallel resistive-fuse network LSI

(including region extraction circuit) (Latest version: March, 2007)